CPLDを動かす1

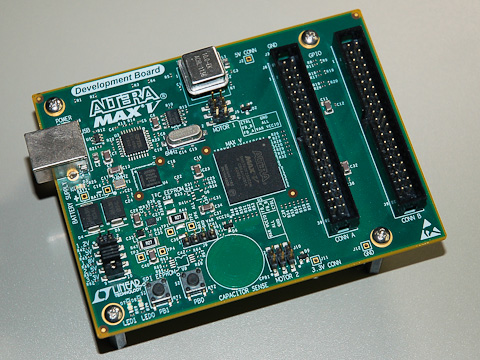

7/20のセミナー「これからはじめるロジック回路」ではCPLDを取り上げました.もともとは74HCシリーズを使っての実験を考えていましたが,よくよく考えるととても地味です.また今の時代はCPLDやFPGAが主流なので,今回はCPLDでロジック回路を組む内容にしました.セミナーで使ったのはintel社(altera)のMAX V CPLD Development Kit.これ75ドルほどで売られています.

ボードにはタクトSWが2個とLEDが2個乗っており,ビギナー向けの教材としては最高です.回路図などの資料は下記から無料でDLできます.

https://www.intel.co.jp/content/www/jp/ja/programmable/products/boards_and_kits/dev-kits/altera/kit-max-v.html

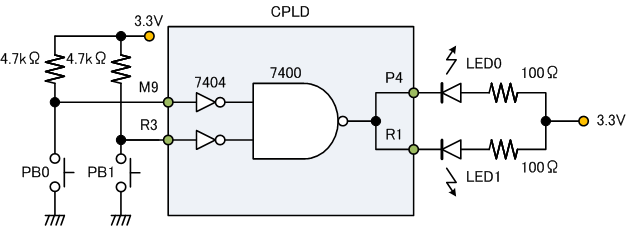

さっそく回路図からCPLDのピンとタクトSWとLEDへの接続を読み込み,次の回路をCPLD内に作成する事にします.

開発ツールはintel社のHPからQuartus Prim Lite Editionをインストールします.これも無料です.サイズは結構大きいのでご注意ください.インストールの方法はネットに詳しい解説がゴロゴロあります.

http://fpgasoftware.intel.com/?edition=lite

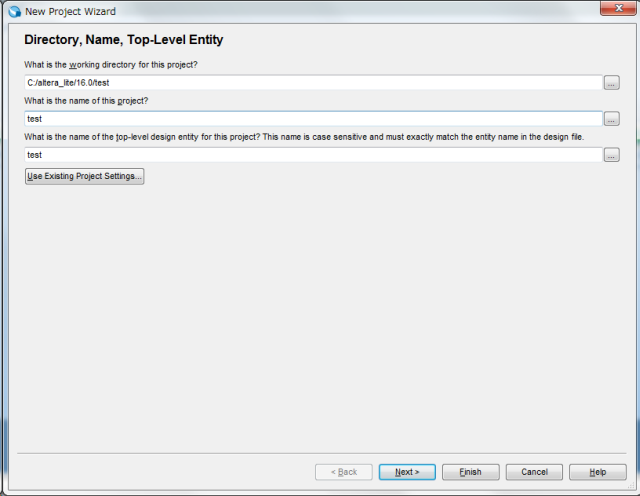

1,プロジェクトを作る

Quartusの「File」「New Project Wizard」からプロジェクトを作成します.今回は「test」というフォルダを作成しその中に全てを展開します.プロジェクトネームもそのまま「test」とました.

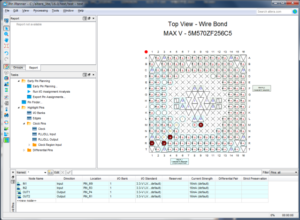

「Next」でどんどん進みデバイスの設定のみを行いました.デバイスはMAX Vの5M570ZF256C5です.さらに「Next」で進み「Finish」でフレームワークを作り終えます.

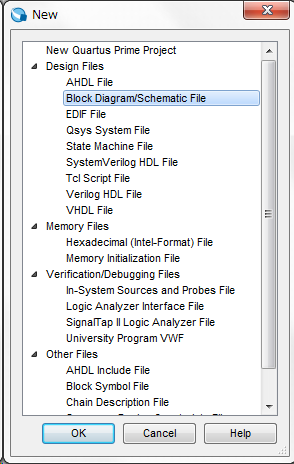

2,回路を作成する

Quartusの「File」「New Block_Diagram/Schematic_File」から回路図CADを立ち上げます.

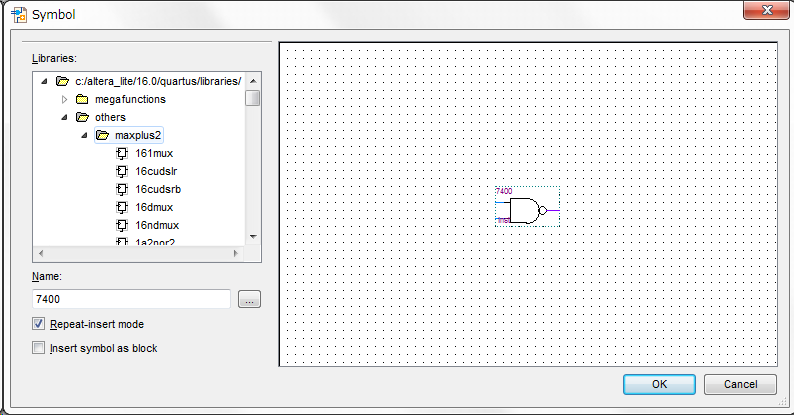

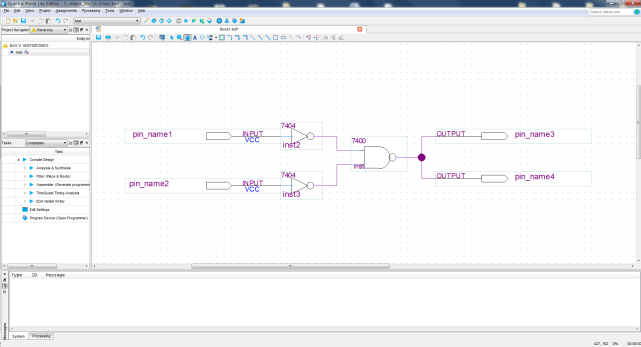

CADメニューの「Symbol Tool」アイコンをクリックして,「Libraries」「others」「maxpluse2」と進んで,ANDの7400やインバータの7404を選びキャンバスに配置します.そして配線ツールを使って配線します.

次にCADメニューの「Pin Tool」アイコンをクリックして,入出力ピンを配置します.

7400と7404のinstは部品名です.これをクリックしてU1~3などの使い慣れたネームに変更すると良いでしょう.同じく入出力ピンをクリックしてIN1,IN2,OUT1,OUT2など,これも解りやすいネームにすると良いでしょう.

Quartusメニューに戻って「start analysis synthesis」アイコンをクリックし軽く組み立てます.組み立ての状況は「Tasks」画面で確認できます.もしも表示されていない場合は「view」「Utility Windows」の中にあり,表示さる事ができます.

つづく